# ITM-MV8-ANT / ITM-DV8

ITM-DV8

ITM-MV8-ANT

Datasheet

(Preliminary)

V0.3

# **Revision History**

| Date       | Revision Content                                                                        | Revised By | Version |

|------------|-----------------------------------------------------------------------------------------|------------|---------|

| 2022/07/06 | - Initial released (Preliminary)                                                        | Marco Liu  | 0.1     |

| 2022/08/19 | - Add Functional Description                                                            | HW         | 0.2     |

| 2022/12/28 | <ul><li>1. Layout Recommendation</li><li>2. Add wakeup Functional Description</li></ul> | HW         | 0.3     |

|            | -                                                                                       |            |         |

|            | -                                                                                       |            |         |

# Contents

| Re | vision Hist | tory                                        | 1  |

|----|-------------|---------------------------------------------|----|

| Сс | ontents     |                                             | 2  |

| 1. | General D   | escription                                  | 6  |

| 2. | Features    |                                             | 7  |

|    | 2.1 ITM-M   | V8-ANT (Module for Mouse Side)              | 7  |

|    |             | V8 (USB Dongle PCBA)                        |    |

| 3. | General S   | pecification                                | 9  |

|    | 0           | es                                          |    |

|    |             | bsolute Maximum Ratings                     |    |

|    | 3.1.2 R     | ecommended Operating Ratings                | 9  |

|    |             | ss Specification (RX)                       |    |

|    | 3.3 Wireles | ss Specification (TX)                       | 10 |

|    |             | Consumption                                 |    |

| 4. |             | Il Description                              |    |

|    |             | Arm® Cortex® -M4F Core                      |    |

|    |             | System Manager                              |    |

|    | 4.2.1       | Overview                                    |    |

|    | 4.2.2       | System Reset                                |    |

|    | 4.2.3       | System Power Distribution                   |    |

|    | 4.2.4       | Power Modes and Wake-up Sources             |    |

|    | 4.2.5       | Power Modes and Power Level Transition      |    |

|    | 4.2.6       | System Memory Map                           |    |

|    | 4.2.7       | SRAM Memory Organization                    |    |

|    | 4.2.8       | HIRC Auto Trim                              |    |

|    | 4.2.9       | Register Lock Control                       |    |

|    | 4.2.10      | System Timer (SysTick)                      |    |

|    | 4.2.11      | Nested Vectored Interrupt Controller (NVIC) |    |

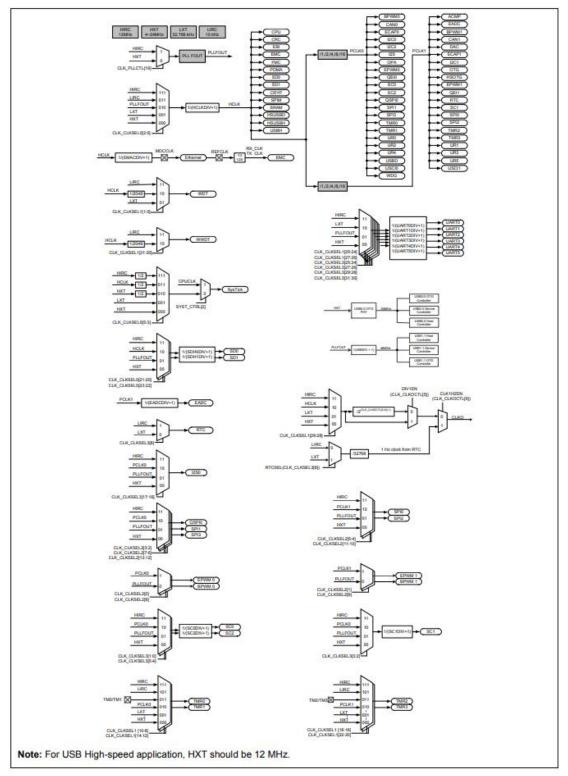

|    | 4.3 (       | Overview                                    |    |

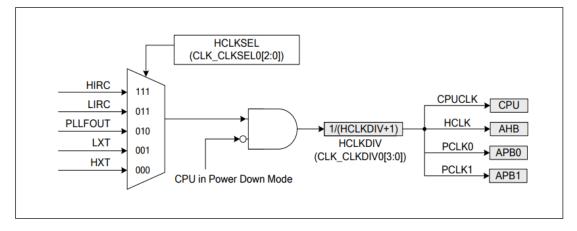

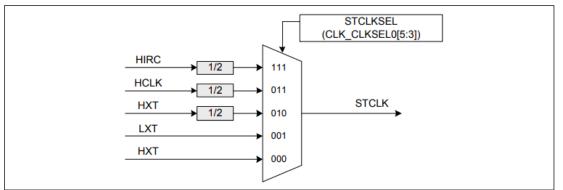

|    | 4.3.1       | Clock Generator                             | -  |

|    | 4.3.2       | System Clock and SysTick Clock              |    |

|    | 4.3.4       | Peripherals Clock                           |    |

|    | 4.3.5       | Power-down Mode Clock                       |    |

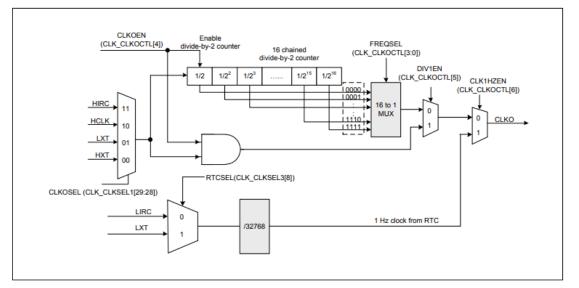

|    | 4.3.6       | Clock Output                                |    |

|    |             | True Random Number Generator (TRNG)         |    |

|    | 4.4.1       | Overview                                    |    |

| 4.4.2 | 2    | Features                                    | 43 |

|-------|------|---------------------------------------------|----|

| 4.5   | Fla  | sh Memory Controller (FMC)                  |    |

| 4.5.1 | 1    | Overview                                    | 43 |

| 4.5.2 | 2    | Features                                    | 43 |

| 4.6   | Ge   | neral Purpose I/O (GPIO)                    |    |

| 4.6.1 | 1    | Overview                                    | 45 |

| 4.6.2 | 2    | Features                                    | 45 |

| 4.7   | PD   | MA Controller (PDMA)                        |    |

| 4.7.1 | 1    | Overview                                    |    |

| 4.7.2 | 2    | Features                                    |    |

| 4.8   | Tim  | ner Controller (TMR)                        |    |

| 4.8.1 | 1    | Overview                                    |    |

| 4.8.2 | 2    | Features                                    | 47 |

| 4.8.2 | 2.1  | Timer Function Features                     |    |

| 4.8.2 | 2.2  | PWM Function Features                       |    |

| 4.9   | Wa   | tchdog Timer (WDT)                          |    |

| 4.9.1 | 1    | Overview                                    |    |

| 4.9.2 | 2    | Features                                    |    |

| 4.10  | Wir  | ndow Watchdog Timer (WWDT)                  |    |

| 4.10  | .1   | Overview                                    |    |

| 4.10  | .2   | Features                                    |    |

| 4.11  | Rea  | al Time Clock (RTC)                         |    |

| 4.11  | .1   | Overview                                    |    |

| 4.11  | .2   | Features                                    |    |

| 4.12  | EP   | WM Generator and Capture Timer (EPWM)       |    |

| 4.12  | .1   | Overview                                    | 50 |

| 4.12  | .2   | Features                                    | 50 |

| 4.12  | .2.1 | EPWM Function Features                      | 50 |

| 4.12  | .2.2 | Capture Function Features                   | 51 |

| 4.13  | Bas  | sic PWM Generator and Capture Timer (BPWM)  |    |

| 4.13  | .1   | Overview                                    | 52 |

| 4.13  | .2   | Features                                    |    |

| 4.13  | .2.1 | BPWM Function Features                      |    |

| 4.13  | .2.2 | Capture Function Features                   | 52 |

| 4.14  | Qua  | adrature Encoder Interface (QEI)            | 53 |

| 4.14  | .1   | Overview                                    | 53 |

| 4.14  | .2   | Features                                    | 53 |

| 4.14  | .2.1 | Quadrature Encoder Interface (QEI) Features | 53 |

| 4.15  | Enł  | nanced Input Capture Timer (ECAP)           | 54 |

| 4.15. | 1 Overview                                                      | 54 |

|-------|-----------------------------------------------------------------|----|

| 4.15. | 2 Features                                                      | 54 |

| 4.16  | UART Interface Controller (UART)                                | 54 |

| 4.16. | 1 Overview                                                      | 54 |

| 4.16. | 2 Features                                                      | 54 |

| 4.17  | Serial Peripheral Interface (SPI)                               | 56 |

| 4.17. | 1 Overview                                                      | 56 |

| 4.17. | 2 Features                                                      | 56 |

| 4.18  | Quad Serial Peripheral Interface (QSPI)                         | 57 |

| 4.18. | 1 Overview                                                      | 57 |

| 4.18. | 2 Features                                                      | 57 |

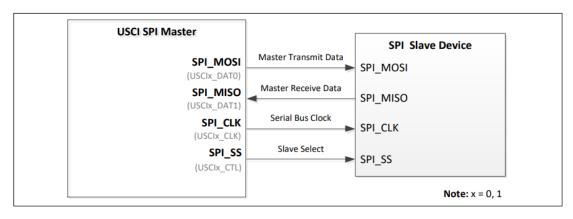

| 4.19  | SPI Synchronous Serial Interface Controller (SPI Master mode)   | 58 |

| 4.19. | 1 Overview                                                      | 58 |

| 4.19. | 2 Features                                                      | 59 |

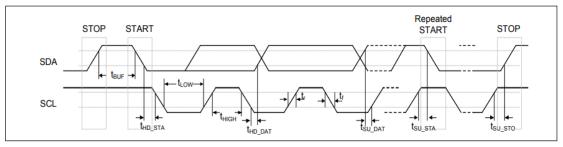

| 4.20  | I <sup>2</sup> C Serial Interface Controller (I <sup>2</sup> C) | 59 |

| 4.20. | 1 Overview                                                      | 59 |

| 4.20. | 2 Features                                                      | 59 |

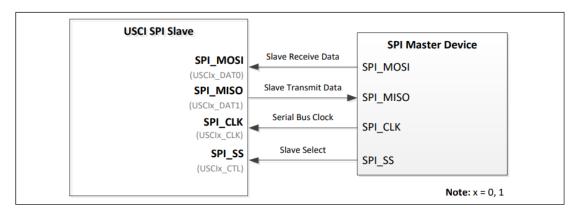

| 4.21  | USCI - Universal Serial Control Interface Controller (USCI)     | 60 |

| 4.21. | 1 Overview                                                      | 60 |

| 4.21. | 2 Features                                                      | 60 |

| 4.22  | USCI – UART Mode                                                | 61 |

| 4.22. | 1 Overview                                                      | 61 |

| 4.22. | 2 Features                                                      | 61 |

| 4.23  | USCI - SPI Mode                                                 | 61 |

| 4.23. | 1 Overview                                                      | 61 |

| 4.23. | 2 Features                                                      | 62 |

| 4.24  | USCI - I <sup>2</sup> C Mode                                    | 63 |

| 4.24. | 1 Overview                                                      | 63 |

| 4.24. | 2 Features                                                      | 63 |

| 4.25  | USB 1.1 Device Controller (USBD)                                | 64 |

| 4.25. | 1 Overview                                                      | 64 |

| 4.25. | 2 Features                                                      | 64 |

| 4.26  | High Speed USB 2.0 Device Controller (HSUSBD)                   | 65 |

| 4.26. | 1 Overview                                                      | 65 |

| 4.26. | 2 Features                                                      | 65 |

| 4.27  | CRC Controller (CRC)                                            | 65 |

| 4.27. | 1 Overview                                                      | 65 |

| 4.27. | 2 Features                                                      | 66 |

| 4.28  | Enhanced 12-bit Analog-to-Digital Converter (EADC)              | 66 |

|    | 4.28.1    |          | Overview                                             | 66 |

|----|-----------|----------|------------------------------------------------------|----|

|    | 4.28.2    | <u> </u> | Features                                             | 66 |

|    | 4.29      | Dig      | ital to Analog Converter (DAC)                       | 67 |

|    | 4.29.1    |          | Overview                                             | 67 |

|    | 4.29.2    | 2        | Features                                             | 68 |

|    | 4.30      | Ana      | alog Comparator Controller (ACMP)                    | 68 |

|    | 4.30.1    |          | Overview                                             | 68 |

|    | 4.30.2    | <u>-</u> | Features                                             | 68 |

|    | 4.31      | Am       | plifier (OPA)                                        | 69 |

|    | 4.31.1    |          | Overview                                             | 69 |

|    | 4.31.2    | <u>-</u> | Features                                             | 69 |

|    | 4.32      | Per      | ipherals Interconnection                             | 69 |

|    | 4.32.1    |          | Overview                                             | 69 |

|    | 4.32.2    | <u>-</u> | Peripherals Interconnect Matrix Table                | 70 |

|    | 4.32.3    | 5        | Functional Description                               | 70 |

|    | 4.32.3    | 8.1      | From EPWM, TIMER to EADC/DAC                         | 70 |

|    | 4.32.3    | 8.2      | From LXT and USB 1.1 Device to HIRC TRIM & RC 48 MHz | 71 |

|    | 4.32.3    | 3.3      | From EPWM/ BPWM to EPWM/ BPWM                        | 72 |

|    | 4.32.3    | 8.4      | From TIMER to EPWM/BPWM                              | 72 |

|    | 4.32.3    | 8.5      | From ACMP and LIRC to Timer Capture Function         | 72 |

|    | 4.32.3    | 8.6      | From Timer0/2 to Timer1/3                            | 73 |

|    | 4.32.3    | 8.7      | From QEI to ECAP                                     | 73 |

|    | 4.32.3    | 8.8      | From TIMER to QEI                                    | 73 |

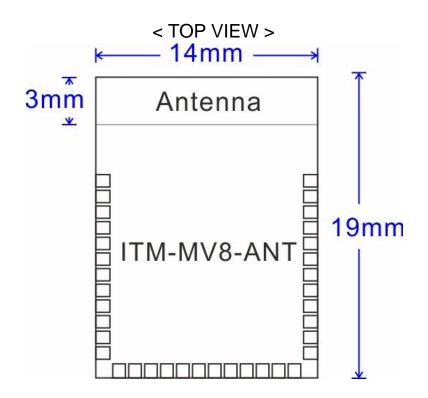

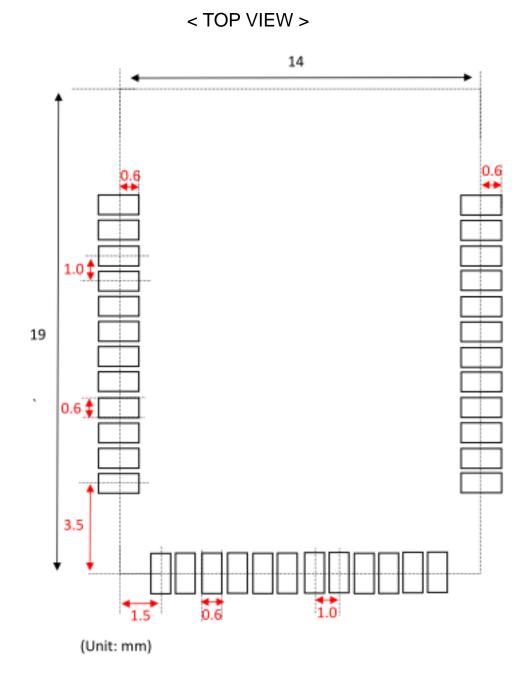

| 5. | Pin Assig | gnm      | ents                                                 | 74 |

|    | 5.1 PCB I | Pin (    | Dutline                                              | 74 |

|    | 5.2 Pin D | efinit   | tion                                                 | 75 |

|    | 5.3 Pin C | onfig    | guration (ITM-MV8-ANT)                               | 76 |

| 6. | Dimensio  | ons.     |                                                      | 85 |

|    | 6.1 Layou | ut Re    | ecommendation                                        | 85 |

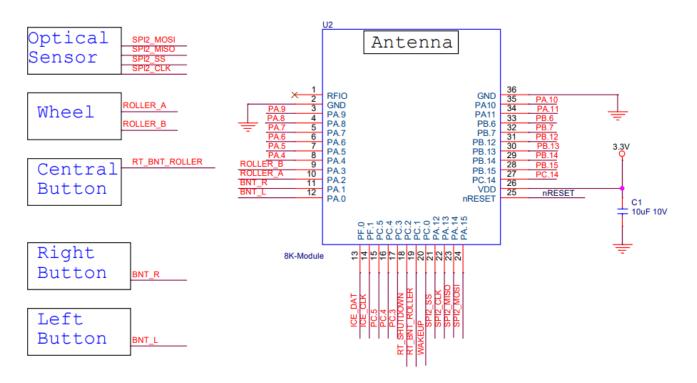

| 7. | Referenc  | e De     | əsign                                                | 86 |

|    | 7.1 ITM-N | /IV8-    | ANT                                                  | 86 |

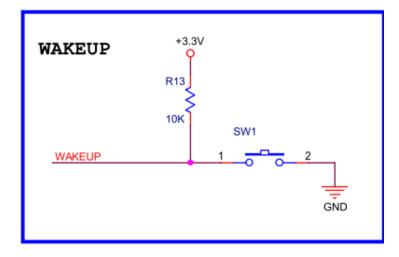

|    | 7.2 ITM-N | /IV8     | series module External Wake Up from Deep Sleep       | 86 |

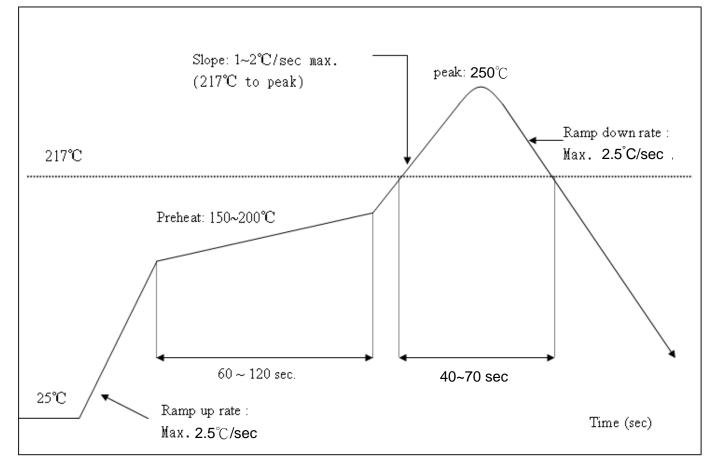

| 8. | Recomm    | end      | ed Reflow Profile                                    | 87 |

# 1. General Description

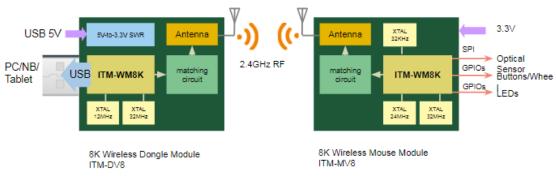

ITM-MV8-ANT and ITM-DV8 use Brickcom RF chipset ITM-WM8K to implement the world-wide first wireless mouse solution up to 8KHz polling rate. ITM-MV8-ANT is the module PCBA designed for the mouse side, connected to optical sensor, buttons, wheel, LEDs and 3.3V power source. ITM-DV8 is an USB dongle PCBA designed for the PC/NB side, to transmit/receive data to/from ITM-MV8-ANT. Via USB2.0 HS, ITM-DV8 can transfer mouse data from ITM-MV8-ANT to PC/NB with maximum 8KHz polling rate.

Block diagram of ITM-MV8-ANT / ITM-DV8

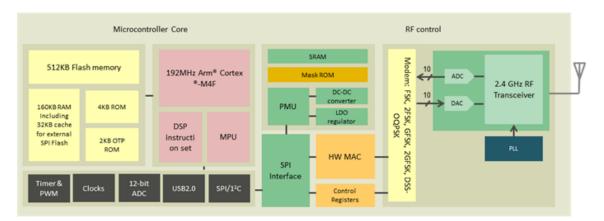

Block diagram of ITM-WM8K (USB2.0 feature is only available for ITM-DV8)

# 2. Features

### 2.1 ITM-MV8-ANT (Module for Mouse Side)

- Main Chipset: ITM-WM8K

- MCU

- ARM® Cortex®- M4F 32-bit processor, running up to 192 MHz

- Built-in Memory Protection Unit (MPU)

- Built-in Nested Vectored Interrupt Controller (NVIC)

- ◆ Hardware IEEE 754 compliant Floating-point Unit (FPU)

- DSP extension with hardware divider and single-cycle 32-bit hardware multiplier

- ◆ 24-bit system tick timer / 32-bit Timer \*4

- Programmable and maskable interrupt

- Low Power Sleep mode by WFI and WFE instructions

- Memory

- 512KB flash and 160KB (include 32 KB cache for XIP) RAM

- ♦ 4KB ISP Loader ROM

- Security

- 96-bit Unique ID (UID)

- ◆ 128-bit Unique Customer ID (UCID).

- One built-in temperature sensor with 1°C resolution.

- Wireless

- 2.4GHz-2.5GHz proprietary RF transceiver

- ◆ -20 to +10 dBm configurable TX power

- -96 dB sensitivity at 1Mbps data rate

- -93 dBm sensitivity at 2Mbps data rate

- -87 dBm sensitivity at 4Mbps data rate

- GPIOs

- Total 28 GPIOs available

- Support SPI/UART/I<sup>2</sup>C/ADC function

- Antenna

- Built-in chip antenna (Dimension L x W: 8.0X1.0mm)

- External antenna can be connected when not using built-in antenna

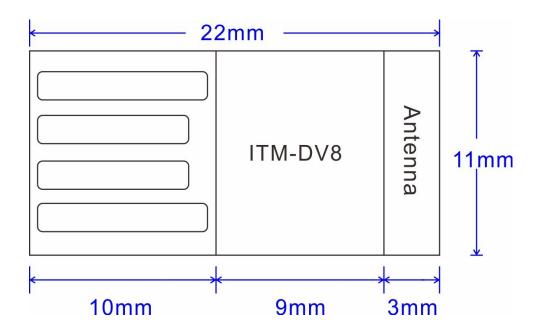

### 2.2 ITM-DV8 (USB Dongle PCBA)

- Main Chipset : ITM-WM8K

- MCU

- ARM® Cortex®- M4F 32-bit processor, running up to 192 MHz

- Built-in Memory Protection Unit (MPU)

- Built-in Nested Vectored Interrupt Controller (NVIC)

- Hardware IEEE 754 compliant Floating-point Unit (FPU)

- DSP extension with hardware divider and single-cycle 32-bit hardware multiplier

- ◆ 24-bit system tick timer / 32-bit Timer \*4

- Programmable and maskable interrupt

- Low Power Sleep mode by WFI and WFE instructions

- Memory

- 512KB flash and 160KB (include 32 KB cache for XIP) RAM

- ♦ 4KB ISP Loader ROM

- Security

- 96-bit Unique ID (UID)

- ◆ 128-bit Unique Customer ID (UCID).

- One built-in temperature sensor with 1°C resolution.

- Wireless

- 2.4GHz-2.5GHz proprietary RF transceiver

- -20 to +10 dBm configurable TX power

- -96 dBm sensitivity at 1Mbps data rate

- -93 dBm sensitivity at 2Mbps data rate

- ◆ -87 dBm sensitivity at 4Mbps data rate

- USB

- USB Specification reversion 2.0 compliant

- Supports 12 configurable endpoints in addition to Control Endpoint

- Supports DMA operation

- ◆ 4092 Bytes Configurable RAM used as endpoint buffer

- Supports Endpoint Maximum Packet Size up to 1024 bytes

- Antenna

- Built-in chip antenna

- Power Supply

- 4.5V~5.5V from USB bus power; Built-in 5V-to-3.3V switching LDO

# 3. General Specification

## 3.1 Voltages

### 3.1.1 Absolute Maximum Ratings

### ITM-MV8-ANT

| Symbol | Description          | Min. | Max. | Unit |

|--------|----------------------|------|------|------|

| VDD    | Input supply Voltage | -0.3 | 3.6  | V    |

|        |                      |      |      |      |

### ITM-DV8

| Symbol | Description          | Min. | Max. | Unit |

|--------|----------------------|------|------|------|

| VDD    | Input supply Voltage | -0.3 | 5.8  | V    |

|        |                      |      |      |      |

### 3.1.2 Recommended Operating Ratings

### ITM-MV8-ANT

| Test conditions: At operating temperature 0°C ~ 70°C |      |      |      |      |  |

|------------------------------------------------------|------|------|------|------|--|

| Symbol                                               | Min. | Тур. | Max. | Unit |  |

| VDD                                                  | 3.0  | 3.3  | 3.6  | V    |  |

### ITM-DV8

| Test conditions: At operating temperature 0°C ~ 70°C |      |      |      |      |  |

|------------------------------------------------------|------|------|------|------|--|

| Symbol                                               | Min. | Тур. | Max. | Unit |  |

| VDD                                                  | 4.5  | 5.0  | 5.5  | V    |  |

## 3.2 Wireless Specification (RX)

| Parameters                    | Conditions | Min. | Тур. | Max. | Unit |

|-------------------------------|------------|------|------|------|------|

| Frequency Range               |            | 2400 |      | 2500 | MHz  |

|                               | 1Mbps      |      | -96  |      | dBm  |

| RX Sensitivity<br>< 30.8% PER | 2Mbps      |      | -93  |      | dBm  |

| < 30.0% PER                   | 4Mbps      |      | -87  |      | dBm  |

| Maximum Input Level           |            |      | 0    |      | dBm  |

## 3.3 Wireless Specification (TX)

| Parameters           | Conditions | Min. | Тур. | Max. | Unit |

|----------------------|------------|------|------|------|------|

| Frequency Range      |            | 2400 |      | 2500 | MHz  |

| Maximum Output Power |            |      | 10   |      | dBm  |

| Power Control Range  |            | -20  |      | 10   | dB   |

## 3.4 Power Consumption

## ITM-MV8-ANT

| Active Mode @ 8KHz Report Rate                                                     | 16.4 mA           | (Typical)              |

|------------------------------------------------------------------------------------|-------------------|------------------------|

| Low Power Mode:<br>Deep LPS (Wakeup by GPIO/Timer)<br>Power Down (Wakeup by RESET) | < 100uA<br>< 50uA | (Typical)<br>(Typical) |

## ITM-DV8

| Active Mode @ 8KHz Report Rate | 35.0mA | (Typical) |

|--------------------------------|--------|-----------|

| Standby Mode                   | 100uA  | (Typical) |

# 4. Functional Description

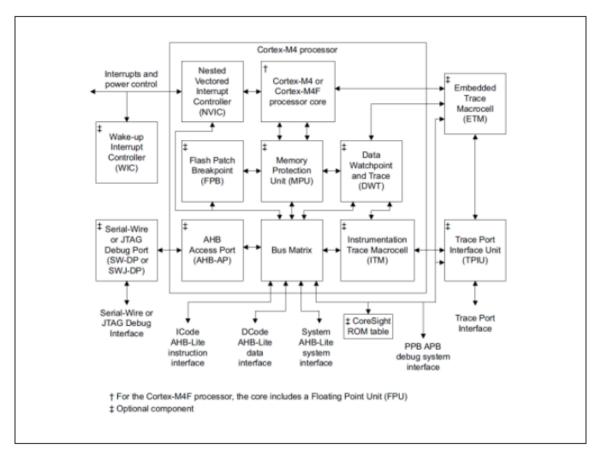

### 4.1 Arm® Cortex® -M4F Core

The Cortex®-M4 processor, a configurable, multistage, 32-bit RISC processor, has three AMBA AHB- Lite interfaces for best parallel performance and includes an NVIC component. The processor with optional hardware debug functionality can execute Thumb code and is compatible with other Cortex®- M profile processors. The profile supports two modes -Thread mode and Handler mode. Handler mode is entered as a result of an exception. An exception return can only be issued in Handler mode. Thread mode is entered on Reset, and can be entered as a result of an exception return. The Cortex®- M4F is a processor with the same capability as the Cortex®-M4 processor and includes floating point arithmetic functionality. The ITM-MV8 series is embedded with Cortex®-M4F processor. Throughout this document, the name Cortex®-M4 refers to both Cortex®-M4 and Cortex®-M4F processor.

Figure 4.1-1 Cortex®-M4F Block Diagram

### Cortex® -M4F processor features:

A low gate count processor core, with low latency interrupt processing that has:

- A subset of the Thumb instruction set, defined in the Armv7-M Architecture Reference

Manual

- Banked Stack Pointer (SP)

- Hardware integer divide instructions, SDIV and UDIV

- Handler and Thread modes

- Thumb and Debug states

- Support for interruptible-continued instructions LDM, STM, PUSH, and POP for low interrupt latency

- Automatic processor state saving and restoration for low latency Interrupt Service Routine (ISR) entry and exit

- Support for Armv6 big-endian byte-invariant or little-endian accesses

- Support for Armv6 unaligned accesses

- Floating Point Unit (FPU) in the Cortex®-M4F processor providing:

- 32-bit instructions for single-precision (C float) data-processing operations

- Combined Multiply and Accumulate instructions for increased precision (Fused MAC)

- Hardware support for conversion, addition, subtraction, multiplication with optional accumulate, division, and square-root

- Hardware support for denormals and all IEEE rounding modes

- 32 dedicated 32-bit single precision registers, also addressable as 16 double-word registers

- Decoupled three stage pipeline

- Nested Vectored Interrupt Controller (NVIC) closely integrated with the processor core to achieve low latency interrupt processing. Features include:

- External interrupts. Configurable from 1 to 240 (the ITM-MV8 series configured with 64 interrupts)

- Bits of priority, configurable from 3 to 8

- Dynamic reprioritization of interrupts

- Priority grouping which enables selection of preempting interrupt levels and nonpreempting interrupt levels

- Support for tril-chaining and late arrival of interrupts, which enables back-to-back interrupt processing without the overhead of state saving and restoration between interrupts.

- Processor state automatically saved on interrupt entry, and restored on interrupt exit with on instruction overhead

- Support for Wake-up Interrupt Controller (WIC) with Ultra-low Power Sleep mode

- Memory Protection Unit (MPU). An optional MPU for memory protection, including:

- Eight memory regions

- Sub Region Disable (SRD), enabling efficient use of memory regions

- The ability to enable a background region that implements the default memory map

attributes

- Low-cost debug solution that features:

- Debug access to all memory and registers in the system, including access to memory mapped devices, access to internal core registers when the core is halted, and access to debug control registers even while SYSRESETn is asserted.

- Serial Wire Debug Port(SW-DP) or Serial Wire JTAG Debug Port (SWJ-DP) debug access

- Optional Flash Patch and Breakpoint (FPB) unit for implementing breakpoints and

- code patches

- Optional Data Watchpoint and Trace (DWT) unit for implementing watchpoints, data tracing, and system profiling

- Optional Instrumentation Trace Macrocell (ITM) for support of printf() style debugging

- Optional Trace Port Interface Unit (TPIU) for bridging to a Trace Port Analyzer (TPA), including Single Wire Output (SWO) mode

- Optional Embedded Trace Macrocell (ETM) for instruction trace.

- Bus interfaces:

- Three Advanced High-performance Bus-Lite (AHB-Lite) interfaces: ICode, Dcode, and System bus interfaces

- Private Peripheral Bus (PPB) based on Advanced Peripheral Bus (APB) interface

- Bit-band support that includes atomic bit-band write and read operations.

- Memory access alignment

- Write buffer for buffering of write data

- Exclusive access transfers for multiprocessor systems

### 4.2 System Manager

4.2.1 Overview

System management includes the following sections:

- System Reset

- System Power Distribution

- SRAM Memory Organization

- System Timer (SysTick)

- Nested Vectored Interrupt Controller (NVIC)

- System Control register

- 4.2.2 System Reset

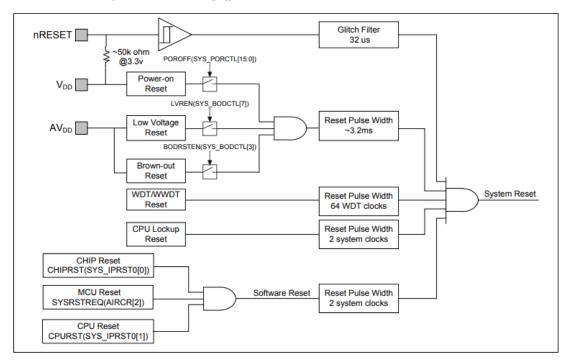

The system reset can be issued by one of the events listed below. These reset event flags can be read from SYS\_RSTSTS register to determine the reset source.

Hardware reset sources are from peripheral signals. Software reset can trigger reset through setting control registers.

- Hardware Reset Sources

- Power-on Reset

- Low level on the nRESET pin

- Watchdog Time-out Reset and Window Watchdog Reset (WDT/WWDT Reset)

- Low Voltage Reset (LVR)

- Brown-out Detector Reset (BOD Reset)

- CPU Lockup Reset

- Software Reset Sources

- CHIP Reset will reset whole chip by writing 1 to CHIPRST (SYS\_IPRST0[0])

- MCU Reset to reboot but keeping the booting setting from APROM or LDROM by writing 1 to SYSRESETREQ (AIRCR[2])

- CPU Reset for Cortex®-M4 core only by writing 1 to CPURST (SYS\_IPRST0[1])

Figure 4.2-1 System Reset Sources

There are a total of 9 reset sources in the family. In general, CPU reset is used to reset Cortex®-M4 only; the other reset sources will reset Cortex®-M4 and all peripherals. However, there are small differences between each reset source and they are listed in Table 4.2-1.

| Reset Sources<br>Register   | POR                | nRESET             | WDT                | LVR                | BOD                | Lockup             | CHIP               | MCU                | CPU       |

|-----------------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|-----------|

| SYS_RSTSTS                  | Bit 0 = 1          | Bit 1 = 1          | Bit 2 = 1          | Bit 3 = 1          | Bit 4 = 1          | Bit 8 = 1          | Bit 0 = 1          | Bit 5 = 1          | Bit 7 = 1 |

| CHIPRST                     | 0x0                | -                  | -                  | -                  | -                  | -                  | -                  | -                  | -         |

| (SYS_IPRST0[0])             |                    |                    |                    |                    |                    |                    |                    |                    |           |

| BODEN<br>(SYS_BODCTL[0])    | Reload<br>from     | Reload<br>from     | Reload<br>from     | Reload<br>from     | -                  | Reload<br>from     | Reload<br>from     | Reload<br>from     | -         |

| BODVL<br>(SYS_BODCTL[2:1])  |                    | CONFIG0            |                    |                    |                    | CONFIG0            |                    |                    |           |

| BODRSTEN                    |                    |                    |                    |                    |                    |                    |                    |                    |           |

| (SYS_BODCTL[3])             |                    |                    |                    |                    |                    |                    |                    |                    |           |

| HXTEN                       | Reload             |           |

| (CLK_PWRCTL[0])             | from               |           |

|                             | CONFIG0            |           |

| LXTEN<br>(CLK_PWRCTL[1])    | 0x0                | -                  | -                  | -                  | -                  | -                  | -                  | -                  | -         |

| WDTCKEN<br>(CLK_APBCLK0[0]) | 0x1                | -                  | 0x1                | -                  | -                  | -                  | 0x1                | -                  | -         |

| HCLKSEL                     | Relo<br>ad<br>from | -         |

| (CLK_CLKSEL0[2:             | CON                |           |

| 0])                         | FIG0               |           |

| WDTSEL                      | 0x3                | 0x3                | -                  | -                  | -                  | -                  | -                  | -                  | -         |

| (CLK_CLKSEL1[1:0])          |                    |                    |                    |                    |                    |                    |                    |                    |           |

| HXTSTB<br>(CLK_STATUS[0])   | 0x0                | -                  | -                  | -                  | -                  | -                  | -                  | -                  | -         |

| LXTSTB<br>(CLK_STATUS[1])   | 0x0                | -                  | -                  | -                  | -                  | -                  | -                  | -                  | -         |

| PLLSTB                      | 0x0                | -                  | -                  | -                  | -                  | -                  | -                  | -                  | -         |

| (CLK_STATUS[2])             |                    |                    |                    |                    |                    |                    |                    |                    |           |

| HIRCSTB<br>(CLK_STATUS[4])  | 0x0                | -                  | -                  | -                  | -                  | -                  | -                  | -                  | -         |

| CLKSFAIL<br>(CLK_STATUS[7]) | 0x0                | 0x0                | -                  | -                  | -                  | -                  | -                  | -                  | -         |

| RSTEN<br>(WDT_CTL[1])       | Reload             | Reload             | Reload             | Reload             | Reload             | -                  | Reload             | -                  | -         |

| WDTEN<br>(WDT_CTL[7])       | from<br>CONFIG0    | from<br>CONFIG0    | from<br>CONFIG0    | from<br>CONFIG0    | from<br>CONFIG0    |                    | from<br>CONFIG0    |                    |           |

| WDT_CTL                     | 0x0700             | 0x0700             | 0x0700             | 0x0700             | 0x0700             | -                  | 0x0700             | -                  | -         |

| except bit 1 and bit 7.     | 0x0000             | 0x0000             | 0x0000             | 0x0000             | 0x0000             |                    | 0x0000             |                    |           |

| WWDT_RLDCNT                                                       | 0x0000            | 0x0000            | 0x0000            | 0x0000            | 0x0000            | - | 0x0000            | - | - |

|-------------------------------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|---|-------------------|---|---|

| WWDT_CTL                                                          | 0x3F0800          | 0x3F0800          | 0x3F0800          | 0x3F0800          | 0x3F0800          | - | 0x3F0800          | - | - |

| WWDT_STATUS                                                       | 0x0000            | 0x0000            | 0x0000            | 0x0000            | 0x0000            | - | 0x0000            | - | - |

| WWDT_CNT                                                          | 0x3F              | 0x3F              | 0x3F              | 0x3F              | 0x3F              | - | 0x3F              | - | - |

| BS<br>(FMC_ISPCTL[1])                                             | Reload            | Reload            | Reload            | Reload            | Reload            | - | Reload            | - | - |

| BL<br>(FMC_ISPCTL[16])                                            | from<br>CONFIG0   | from<br>CONFIG0   | from<br>CONFIG0   | from<br>CONFIG0   | from<br>CONFIG0   |   | from<br>CONFIG0   |   |   |

| FMC_DFBA                                                          | Reload<br>from    | Reload<br>from    | Reload<br>from    | Reload<br>from    | Reload<br>from    | - | Reload<br>from    | - | - |

|                                                                   | CONFIG1           | CONFIG1           | CONFIG1           | CONFIG1           | CONFIG1           |   | CONFIG1           |   |   |

| CBS                                                               | Reload            | Reload            | Reload            | Reload            | Reload            | - | Reload            | - | - |

| (FMC_ISPSTS[2:1))                                                 | from              | from              | from              | from              | from              |   | from              |   |   |

|                                                                   | CONFIG0           | CONFIG0           | CONFIG0           | CONFIG0           | CONFIG0           |   | CONFIG0           |   |   |

| VECMAP                                                            | Reload<br>base on | - | Reload<br>base on | - | - |

| (FMC_ISPSTS[23:9])                                                | CONFIG0           | CONFIG0           | CONFIG0           | CONFIG0           | CONFIG0           |   | CONFIG0           |   |   |

| Other Peripheral                                                  | Reset Valu        | Ie                |                   |                   |                   |   |                   |   | - |

| Registers                                                         |                   |                   |                   |                   |                   |   |                   |   |   |

| FMC Registers Reset Value                                         |                   |                   |                   |                   |                   |   |                   |   |   |

| Note: '-'means that the value of register keeps original setting. |                   |                   |                   |                   |                   |   |                   |   |   |

Table 4.2-1 Reset Value of Registers

### 4.2.2.1 nRESET Reset

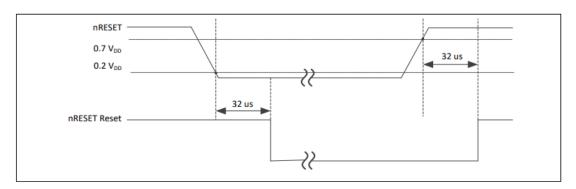

The nRESET reset means to generate a reset signal by pulling low nRESET pin, which is an asynchronous reset input pin and can be used to reset system at any time. When the nRESET voltage is lower than 0.2 VDD and the state keeps longer than 32 us (glitch filter), chip will be reset. The nRESET reset will control the chip in reset state until the nRESET voltage rises above 0.7 VDD and the state keeps longer than 32 us (glitch filter). The PINRF(SYS\_RSTSTS[1]) will be set to 1 if the previous reset source is nRESET reset Figure 4.2-2 shows the nRESET reset waveform.

Figure 4.2-2 nRESET Reset Waveform

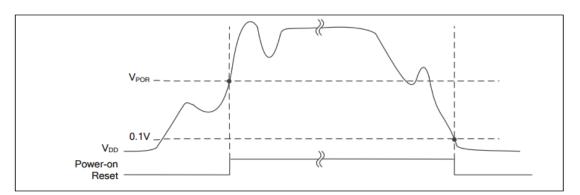

### 4.2.2.2 Power-on Reset (POR)

The Power-on reset (POR) is used to generate a stable system reset signal and forces the system to be reset when power-on to avoid unexpected behavior of MCU. When applying the power to MCU, the POR module will detect the rising voltage and generate reset signal to system until the voltage is ready for MCU operation. At POR reset, the PORF(SYS\_RSTSTS[0]) will be set to 1 to indicate there is a POR reset event. The PORF(SYS\_RSTSTS[0]) bit can be cleared by writing 1 to it. Figure 6.2-3 shows the power-on reset waveform.

Figure 4.2-3 Power-on Reset (POR) Waveform

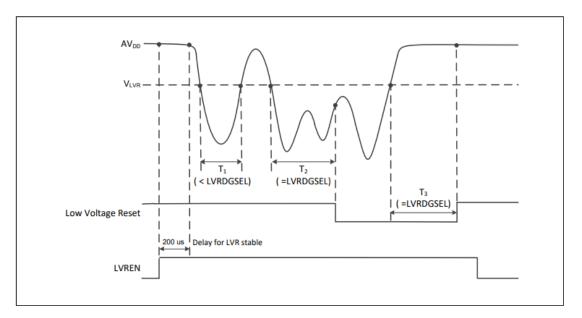

### 4.2.2.3 Low Voltage Reset (LVR)

If the Low Voltage Reset function is enabled by setting the Low Voltage Reset Enable Bit LVREN (SYS\_BODCTL[7]) to 1, after 200us delay, LVR detection circuit will be stable and the LVR function will be active. Then LVR function will detect AVDD during system operation. When the AVDD voltage is lower than VLVR and the state keeps longer than De-glitch time set by LVRDGSEL

(SYS\_BODCTL[14:12]), chip will be reset. The LVR reset will control the chip in reset state until the AVDD voltage rises above VLVR and the state keeps longer than De-glitch time set by LVRDGSEL (SYS\_BODCTL[14:12]). The default setting of Low Voltage Reset is enabled without De-glitch function. Figure 4.2-4 shows the

Low Voltage Reset waveform.

Figure 4.2-4 Low Voltage Reset (LVR) Waveform

### 4.2.2.4 Brown-out Detector Reset (BOD Reset)

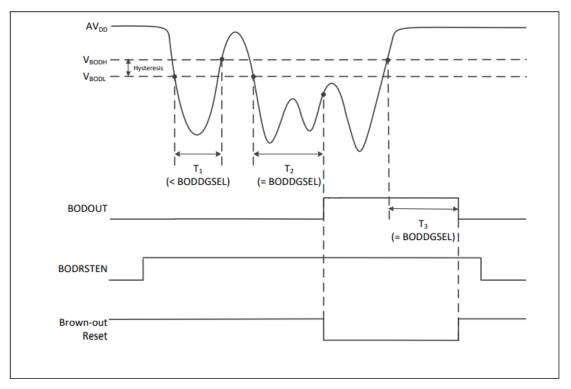

If the Brown-out Detector (BOD) function is enabled by setting the Brown-out Detector Enable Bit BODEN (SYS\_BODCTL[0]), Brown-out Detector function will detect AVDD during system operation. When the AVDD voltage is lower than VBOD which is decided by BODEN and BODVL (SYS\_BODCTL[18:16]) and the state keeps longer than De-glitch time set by BODDGSEL (SYS\_BODCTL[10:8]), chip will be reset. The BOD reset will control the chip in reset state until the AVDD voltage rises above VBOD and the state keeps longer than De-glitch time set by BODDGSEL. The default value of BODEN, BODVL and BODRSTEN (SYS\_BODCTL[3]) is set by Flash controller user configuration register CBODEN (CONFIG0 [19]), CBOV (CONFIG0 [23:21]) and CBORST(CONFIG0[20]) respectively. User can determine the initial BOD setting by setting the CONFIG0 register. Figure 4.2-5 shows the Brown-out Detector waveform.

Figure 4.2-5 Brown-out Detector (BOD) Waveform

### 4.2.2.5 Watchdog Timer Reset (WDT)

In most industrial applications, system reliability is very important. To automatically recover the MCU from failure status is one way to improve system reliability. The watchdog timer(WDT) is widely used to check if the system works fine. If the MCU is crashed or out of control, it may cause the watchdog time-out. User may decide to enable system reset during watchdog time-out to recover the system and take action for the system crash/out-of-control after reset.

Software can check if the reset is caused by watchdog time-out to indicate the previous reset is a watchdog reset and handle the failure of MCU after watchdog time-out reset by checking WDTRF(SYS\_RSTSTS[2]).

### 4.2.2.6 CPU Lockup Reset

CPU enters lockup status after CPU produces hardfault at hardfault handler and chip gives immediate indication of seriously errant kernel software. This is the result of the CPU being locked because of an unrecoverable exception following the activation of the processor's built in system state protection hardware. When chip enters debug mode, the CPU lockup reset will be ignored.

4.2.2.7 CPU Reset, CHIP Reset and MCU Reset

The CPU Reset means only Cortex®-M4 core is reset and all other peripherals remain the same status after CPU reset. User can set the CPURST(SYS\_IPRST0[1]) to 1 to assert the CPU Reset signal.

The CHIP Reset is same with Power-on Reset. The CPU and all peripherals are

reset and BS(FMC\_ISPCTL[1]) bit is automatically reloaded from CONFIG0 setting. User can set the CHIPRST(SYS\_IPRST0[1]) to 1 to assert the CHIP Reset signal. The MCU Reset is similar with CHIP Reset. The difference is that BS(FMC\_ISPCTL[1]) will not be reloaded from CONFIG0 setting and keep its original software setting for booting from APROM or LDROM. User can set the SYSRESETREQ(AIRCR[2]) to 1 to assert the MCU Reset.

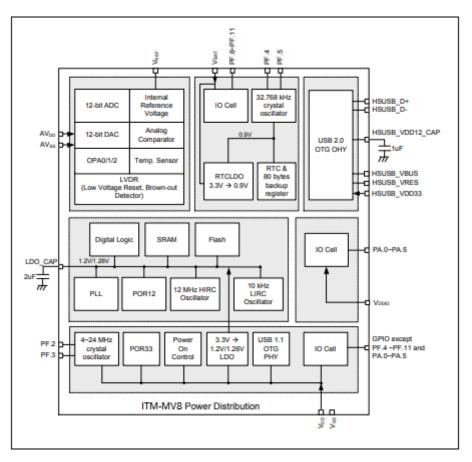

#### 4.2.3 System Power Distribution

In this chip, power distribution is divided into four segments:

- Analog power from AVDD and AVSS provides the power for analog components operation.

- Digital power from VDD and VSS supplies the power to the internal regulator which provides a fixed 1.8 V power for digital operation and I/O pins.

- USB transceiver power from VBUS offers the power for operating the USB transceiver.

- RTC power from VBAT provides the power for RTC and 80 bytes backup registers.

The outputs of internal voltage regulators, LDO and VDD33, require an external capacitor which should be located close to the corresponding pin. Analog power (AVDD) should be the same voltage level of the digital power (VDD). Figure 4.2-6 shows the ITM-MV8 power distribution.

Figure 4.2-6 ITM-MV8-ANT Power Distribution Diagram

Note:

1. When VBAT power source first power-on, the power-on reset will happened and reset all VBAT domain circuit. The I/O in VBAT domain (PF.4 ~ PF.11) will become floating state and make additional leakage in VBAT domain. User should power on VDD first to reset chip and set I/O control to make these I/Os becomes a static state to prevent additional leakage.

2. The VBAT domain I/O (PF.4 ~ PF.11) will have unpredictable 1.5V glitch during power-on if VBAT and VDD connect together. To prevent this unpredictable glitch to make, user should avoid use these pins to be other IC's active or inactive control pins.

#### 4.2.4 Power Modes and Wake-up Sources

The ITM-MV8 series has power manager unit to support several operating modes for saving power. Table 4.2-2 lists all power mode at ITM-MV8 series.

| Mode                                     | CPU Operating Maximum<br>Speed<br>( MHz) | LDO_CAP<br>(V) | Clock Disable                                                                                                                                                  |

|------------------------------------------|------------------------------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Normal mode                              | 160                                      | 1.20           | All clocks are disabled by control register.                                                                                                                   |

| Turbo mode                               | 192                                      | 1.26           | All clocks are disabled by control register.                                                                                                                   |

| Idle mode                                | CPU enter Sleep mode                     | 1.20/1.26      | Only CPU clock is disabled.                                                                                                                                    |

| Fast Wakeup Power-down mode (FWPD)       | CPU enters Deep Sleep mode               | 1.20/1.26      | Most clocks are disabled except LIRC/LXT, and<br>only RTC/WDT/Timer/UART peripheral clocks<br>still enable if their clock sources are selected as<br>LIRC/LXT. |

| Normal Power-down mode<br>(NPD)          | CPU enters Deep Sleep mode               | 1.20/1.26      | Most clocks are disabled except LIRC/LXT, and<br>only RTC/WDT/Timer/UART peripheral clocks<br>still enable if their clock sources are selected as<br>LIRC/LXT. |

| Low leakage Power-down<br>mode<br>(LLPD) | CPU enters Deep Sleep mode               | 0.9            | Most clocks are disabled except LIRC/LXT, and<br>only RTC/WDT/Timer/UART peripheral clocks<br>still enable if their clock sources are selected as<br>LIRC/LXT. |

| Standby Power-down mode<br>(SPD0)        | Power off                                | Floating       | Only LIRC/LXT still enable for RTC function and<br>wake-up timer usage                                                                                         |

| Standby Power-down mode<br>(SPD1)        | Power off                                | Floating       | Only LIRC/LXT still enable for RTC function and<br>wake-up timer usage                                                                                         |

| Deep Power-down mode<br>(DPD)*           | Power off                                | Floating       | Only LIRC/LXT still enable for RTC function and wake-up timer usage                                                                                            |

Table 4.2-2 Power Mode Table

Note:

1. User must turn on LIRC before entering SPD0/1 mode.

2. SPD0 mode has 32KB data retention in SRAM bank0.

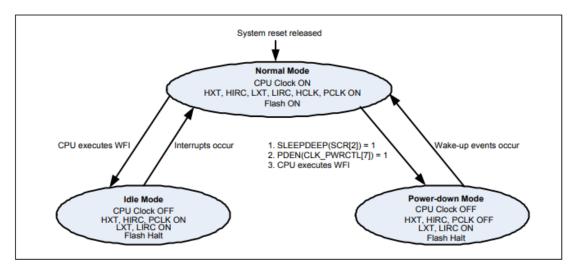

There are different power mode entry setting for each power mode, they have different entry setting and leaving condition. Table 4.2-3 shows the entry setting for each power mode. When chip power-on, chip is running an normal mode. User can enter each mode by setting SLEEPDEEP (SCR[2]), PDEN (CLK\_PWRCT:[7]) and PDMSEL (CLK\_PMUCTL[2:0]) and execute WFI instruction. And

| Register/Instruction<br>Mode | SLEEPDEEP<br>(SCR[2]) | PDEN<br>(CLK_PWRCTL[7]) | PDMSEL<br>(CLK_PMUCTL[2:0]) | CPU Run WFI Instruction |

|------------------------------|-----------------------|-------------------------|-----------------------------|-------------------------|

| Normal mode                  | 0                     | 0                       | 0                           | NO                      |

| Idle mode                    | 0                     | 0                       | 0                           | YES                     |

| Fast Wakeup Power-down mode  | 1                     | 1                       | 2                           | YES                     |

| Normal Power-down mode       | 1                     | 1                       | 0                           | YES                     |

| Low leakage Power-down mode  | 1                     | 1                       | 1                           | YES                     |

| Standby Power-down mode 0    | 1                     | 1                       | 4                           | YES                     |

| Standby Power-down mode 1    | 1                     | 1                       | 5                           | YES                     |

|                              |                       |                         |                             |                         |

| Deep Power-down mode*        | 1                     | 1                       | 6                           | YES                     |

Table 4.2-3 Power Mode Difference Table

There are several wake-up sources in Idle mode and Power-down mode. Table 4.2-4 lists the available clocks for each power mode.

| Power Mode       | Normal Mode                  | ldle Mode                     | Power-Down Mode               |

|------------------|------------------------------|-------------------------------|-------------------------------|

| Definition       | CPU is in active state       | CPU is in sleep state         | CPU is in sleep state and all |

|                  |                              |                               | clocks stop except LXT and    |

|                  |                              |                               | LIRC. SRAM content retender.  |

| Entry Condition  | Chip is in normal mode after | CPU executes WFI instruction. | CPU sets sleep mode enable    |

|                  | system reset released        |                               | and power down enable and     |

|                  |                              |                               | executes WFI instruction.     |

| Wake-up Sources  | N/A                          | All interrupts                | RTC, WDT, I²C, Timer, UART,   |

|                  |                              |                               | BOD, GPIO, EINT, USCI,        |

|                  |                              |                               | USBD, ACMP and BOD.           |

| Available Clocks | All                          | All except CPU clock          | LXT and LIRC                  |

| After Wake-up    | N/A                          | CPU back to normal mode       | CPU back to normal mode       |

Table 4.2-4 Power Mode Definition Table

Figure 4.2-7 Power Mode State Machine

|                | Idle Mode | NPD, LLPD, FWPD     | SPD                 | DPD                   |

|----------------|-----------|---------------------|---------------------|-----------------------|

| НХТ            | ON        | Halt                | Halt                | Halt                  |

| HIRC           | ON        | Halt                | Halt                | Halt                  |

| LXT            | ON        | ON/OFF <sup>1</sup> | ON/OFF <sup>1</sup> | ON/OFF <sup>1</sup>   |

| LIRC           | ON        | ON/OFF <sup>2</sup> | ON/OFF <sup>2</sup> | ON/OFF <sup>2,8</sup> |

| PLL            | ON        | Halt                | Halt                | Halt                  |

| HCLK/PCLK      | ON        | Halt                | Halt                | Halt                  |

| CPU            | Halt      | Halt                | Halt                | Halt                  |

| SRAM retention | ON        | ON                  | ON/OFF <sup>7</sup> | Halt                  |

| FLASH          | ON        | Halt                | Halt                | Halt                  |

| TIMER          | ON        | ON/OFF <sup>3</sup> | ON/OFF <sup>3</sup> | Halt                  |

| WDT            | ON        | ON/OFF <sup>4</sup> | ON/OFF <sup>4</sup> | Halt                  |

| RTC            | ON        | ON/OFF⁵             | ON/OFF⁵             | ON/OFF⁵               |

| UART           | ON        | ON/OFF <sup>6</sup> | ON/OFF <sup>6</sup> | Halt                  |

| Others         | ON        | Halt                | Halt                | Halt                  |

Table 4.2-5 Clocks in Power Modes

Note:

- 1. LXT ON or OFF depends on SW setting in normal mode.

- 2. LIRC ON or OFF depends on S/W setting in normal mode.

- 3. If TIMER clock source is selected as LIRC/LXT and LIRC/LXT is on.

- 4. If WDT clock source is selected as LIRC and LIRC is on.

- 5. If RTC clock source is selected as LXT and LXT is on.

- 6. If UART clock source is selected as LXT and LXT is on.

- 7. SRAM retention size depends on SW setting in normal mode.

- 8. If timer wake up function is disabled, LIRC will be disabled automatically when chip enter DPD mode for power saving.

Wake-up sources in Normal Power-down mode (NPD):

RTC, WDT, I<sup>2</sup>C, Timer, UART, USCI, BOD, EBOD, GPIO, USBD, and ACMP. After chip enters power down, the following wake-up sources can wake chip up to normal mode. Table 4.2-6 lists the condition about how to enter Power-down mode again for each peripheral.

User needs to wait this condition before setting PDEN(CLK\_PWRCTL[7]) and execute WFI to enter Power-down mode.

|                   |                        | Power-Down Mode |     | Mode |                                                       |

|-------------------|------------------------|-----------------|-----|------|-------------------------------------------------------|

| Wake-Up<br>Source | Wake-Up Condition      | NPD/<br>FWPD/   | SPD | DPD  | Re-Entering Power-Down Mode Condition                 |

|                   |                        | LLPD            |     |      |                                                       |

|                   | Brown-Out Detector     | V               | -   | -    | After software writes 1 to clear BODIF                |

|                   | Reset / Interrupt      |                 |     |      | (SYS_BODCTL[4]).                                      |

| BOD               | Brown-Out Detector     | -               | V   | -    | After software writes 1 (CLK_PMUSTS[31]) to clear     |

|                   | Reset                  |                 |     |      | BODWK (CLK_PMUSTS[13]) when SPD mode is<br>entered.   |

|                   |                        | V               | -   | -    | After software writes 1 to clear LVRF                 |

|                   |                        |                 |     |      | (SYS_RSTSTS[3])                                       |

| LVR               | LVR Reset              | -               | V   | -    | After software writes 1 (CLK_PMUSTS[31]) to clear     |

|                   |                        |                 |     |      | LVRWK (CLK_PMUSTS[12]) when SPD mode is               |

|                   |                        |                 |     |      | entered.                                              |

| POR               | POR Reset              | V               | V   | -    | After software writes 1 to clear PORF                 |

|                   |                        |                 |     |      | (SYS_RSTSTS[0])                                       |

| INT               | External Interrupt     | V               | -   | -    | After software write 1 to clear the Px_INTSRC[n] bit. |

| GPIO              | GPIO Interrupt         | V               | -   | -    | After software write 1 to clear the Px_INTSRC[n] bit. |

| GPIO(PA~PD)       | rising or falling edge | -               | V   | -    | After software writes 1 (CLK_PMUSTS[31]) to clear     |

| Wake-up pin       | event, 64-pin          |                 |     |      | GPxWK (CLK_PMUSTS[11:8]) when SPD mode is             |

|                   |                        |                 |     |      | entered.                                              |

| GPIO(PC.0)        | rising or falling edge | -               | -   | V    | After software writes 1 (CLK_PMUSTS[31]) to clear     |

| Wake-up pin       | event, 1-pin           |                 |     |      | PINWK0 (CLK_PMUSTS[0]) when DPD mode is               |

|                   |                        |                 |     |      | entered.                                              |

| GPIO(PC.0/P           | rising or falling edge |   |   |   | After activers writes 4 (CLI/, DMI ISTS[24]) to clear      |

|-----------------------|------------------------|---|---|---|------------------------------------------------------------|

| B.0/PB.2/PB.1         | event, 5-pin           | - | - | V | After software writes 1 (CLK_PMUSTS[31]) to clear          |

|                       |                        |   |   |   | PINWKx (CLK_PMUSTS[6:3] and CLK_PMUSTS[0])                 |

| 2/PF.6) Wake-         |                        |   |   |   | when DPD mode is entered.                                  |

| up pin                |                        |   |   |   |                                                            |

| TIMER                 | Timer Interrupt        | V | - | - | After software writes 1 to clear TWKF                      |

|                       |                        |   |   |   | (TIMERx_INTSTS[1]) and TIF (TIMERx_INTSTS[0]).             |

| Wakeup timer          | Wakeup by wake-up      | - | V | V | After software writes 1 (CLK_PMUSTS[31]) to clear          |

|                       | timer time-out         |   |   |   | TMRWK (CLK_PMUSTS[1]) when SPD or DPD                      |

|                       |                        |   |   |   | mode is entered.                                           |

| WDT                   | WDT Interrupt          | V | - | - | After software writes 1 to clear WKF (WDT_CTL[5])          |

|                       |                        |   |   |   | (Write Protect).                                           |

| RTC                   |                        | V |   |   |                                                            |

| RIG                   | Alarm Interrupt        | v | - | - | After software writes 1 to clear ALMIF                     |

|                       |                        |   |   |   | (RTC_INTSTS[0]).                                           |

|                       | Time Tick Interrupt    | V | - | - | After software writes 1 to clear TICKIF                    |

|                       |                        |   |   |   | (RTC_INTSTS[1]).                                           |

| UART                  |                        | V |   |   |                                                            |

| UART                  | nCTS wake-up           | v | - | - | After software writes 1 to clear CTSWKF                    |

|                       |                        |   |   |   | (UARTx_WKSTS[0]).                                          |

|                       | RX Data wake-up        | V | - | - | After software writes 1 to clear DATWKF                    |

|                       |                        |   |   |   | (UARTx_WKSTS[1]).                                          |

|                       | Received FIFO          | V | - | - | After software writes 1 to clear RFRTWKF                   |

|                       | Threshold Wake-up      |   |   |   | (UARTx_WKSTS[2]).                                          |

|                       |                        |   |   |   |                                                            |

|                       | RS-485 AAD Mode        | V | - | - | After software writes 1 to clear RS485WKF                  |

|                       | Wake-up                |   |   |   | (UARTx_WKSTS[3]).                                          |

|                       | Received FIFO          | V | - | - | After software writes 1 to clear TOUTWKF                   |

|                       | Threshold Time-out     |   |   |   | (UARTx_WKSTS[4]).                                          |

|                       | Wake-up                |   |   |   |                                                            |

| USCI UART             | CTS Toggle             | V | - | - | After software writes 1 to clear WKF                       |

|                       |                        |   |   |   | (UUART_WKSTS[0]).                                          |

| [                     | Data Toggle            | V | - | - | After software writes 1 to clear WKF                       |

|                       |                        |   |   |   | (UUART_WKSTS[0]).                                          |

| 110 g : :2-           | Data toggle            | V | - | - | After software writes 1 to clear WKF                       |

| USCI I <sup>2</sup> C |                        |   |   |   | (UI <sup>2</sup> C_WKSTS[0]).                              |

|                       |                        |   |   |   |                                                            |

|                       | Address match          | V | - | - | After software writes 1 to clear WKAKDONE                  |

|                       |                        |   |   |   | (UI <sup>2</sup> C_PROTSTS[16], then writes 1 to clear WKF |

|                       |                        |   |   |   | (UI <sup>2</sup> C_WKSTS[0]).                              |

| USCI SPI         | SS Toggle                                   | V | - | - | After software writes 1 to clear WKF                                                                                                          |

|------------------|---------------------------------------------|---|---|---|-----------------------------------------------------------------------------------------------------------------------------------------------|

|                  |                                             |   |   |   | (USPI_WKSTS[0]).                                                                                                                              |

| I <sup>2</sup> C | Address match wake-up                       | V | - | - | After software writes 1 to clear WKAKDONE<br>(I <sup>2</sup> C_WKSTS[1]). Then software writes 1 to clear<br>WKIF(I <sup>2</sup> C_WKSTS[0]). |

| USBD             | Remote Wake-up                              | V | - | - | After software writes 1 to clear BUSIF<br>(USBD_INTSTS[0]).                                                                                   |

| ACMP             | Comparator Power-<br>Down Wake-Up Interrupt | V | - | - | After software writes 1 to clear WKIF0<br>(ACMP_STATUS[8]) and WKIF1<br>(ACMP_STATUS[9]).                                                     |

| ACMP             | ACMPO status change                         | - | V | - | After software writes 1 (CLK_PMUSTS[31]) to clear<br>ACMPWK (CLK_PMUSTS[14]) when SPD mode is<br>entered.                                     |

Table 4.2-6 Re-Entering Power-down Mode Condition

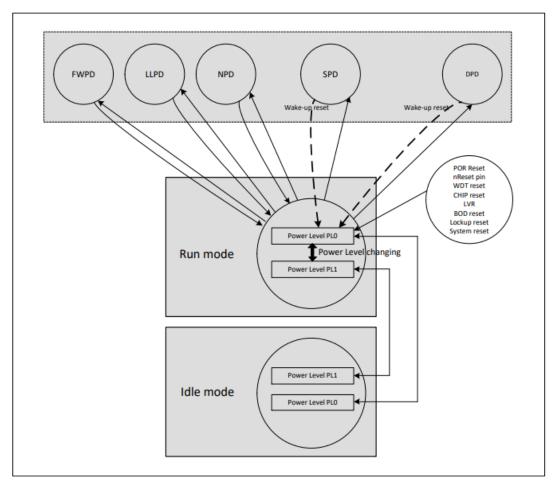

### 4.2.5 Power Modes and Power Level Transition

Figure 4.2-8 ITM-MV8-ANT Power Distribution Diagram

### 4.2.6 System Memory Map

The ITM-MV8 series provides 4G-byte addressing space. The memory locations assigned to each on-chip controllers are shown in Table 4.2-7. The detailed register definition, memory space, and programming will be described in the following sections for each on-chip peripheral. The ITM-MV8 series only supports little-endian data format.

| Address Space                        | Token      | Controllers                                                    |

|--------------------------------------|------------|----------------------------------------------------------------|

| Flash and SRAM Memory Space          |            |                                                                |

| 0x0000_0000 – 0x0003_FFFF            | FLASH_BA   | FLASH Memory Space (256 Kbytes)                                |

| 0x0000_0000 – 0x0007_FFFF            | FLASH_BA   | FLASH Memory Space (512 Kbytes)                                |

| 0x0800_0000 – 0x09FF_FFFF            | SPIM_BA    | SPIM Memory Space (32 Mbytes)                                  |

| 0x2000_0000 – 0x2000_7FFF            | SRAM0_BA   | SRAM Memory Space (32 Kbytes)                                  |

| 0x2000_8000 - 0x2001_FFFF            | SRAM1_BA   | SRAM Memory Space (96 Kbytes)                                  |

| 0x2002_0000 – 0x2002_7FFF            | SRAM2_BA   | SRAM Memory Space (32 Kbytes) for CPU only and share with SPIM |

|                                      |            | cache                                                          |

| 0x6000_0000 – 0x6FFF_FFFF            | EXTMEM_BA  | External Memory Space (256 Mbytes)                             |

| Peripheral Controllers Space (0x4000 |            | FFF)                                                           |

| 0x4000_0000 – 0x4000_01FF            | SYS_BA     | System Control Registers                                       |

| 0x4000_0200 – 0x4000_02FF            | CLK_BA     | Clock Control Registers                                        |

| 0x4000_0300 – 0x4000_03FF            | NMI_BA     | NMI Control Registers                                          |

| 0x4000_4000 – 0x4000_4FFF            | GPIO_BA    | GPIO Control Registers                                         |

| 0x4000_7000 – 0x4000_7FFF            | SPIM_BA    | SPIM Control Registers                                         |

| 0x4000_8000 – 0x4000_8FFF            | PDMA_BA    | Peripheral DMA Control Registers                               |

| 0x4000_9000 – 0x4000_9FFF            | USBH_BA    | USB Host Control Registers                                     |

| 0x4000_C000 – 0x4000_CFFF            | FMC_BA     | Flash Memory Control Registers                                 |

| 0x4000_D000 – 0x4000_DFFF            | SDH0_BA    | SDHOST0 Control Registers                                      |

| 0x4000_E000 – 0x4000_EFFF            | SDH1_BA    | SDHOST1 Control Registers                                      |

| 0x4001_0000 – 0x4001_0FFF            | EBI_BA     | External Bus Interface Control Registers                       |

| 0x4001_9000 – 0x4001_9FFF            | HSUSBD_BA  | HSUSBD Control Registers                                       |

| 0x4001_A000 – 0x4001_AFFF            | HSUSBH _BA | HSUSBH Host Control Registers                                  |

| 0x4003_0000 – 0x4003_0FFF            | CCAP_BA    | CCAP Control Registers                                         |

| 0x4003_1000 – 0x4003_1FFF            | CRC_BA     | CRC Generator Registers                                        |

| 0x4003_E000 – 0x4003_EFFF            | SWDC_BA    | SWD Control Registers                                          |

| 0x4003_F000 – 0x4003_FFFF            | ETMC_BA    | ETM Control Registers                                          |

| 0x5008_0000 – 0x5008_0FFF         | CRYP_BA                                           | Cryptographic Accelerator Registers                           |  |  |  |  |  |

|-----------------------------------|---------------------------------------------------|---------------------------------------------------------------|--|--|--|--|--|

| APB Controllers Space (0x4000_000 | APB Controllers Space (0x4000_0000 ~ 0x400F_FFFF) |                                                               |  |  |  |  |  |

| 0x4004_0000 – 0x4004_0FFF         | WDT_BA                                            | Watchdog Timer Control Registers                              |  |  |  |  |  |

| 0x4004_1000 – 0x4004_1FFF         | RTC_BA                                            | Real Time Clock (RTC) Control Register                        |  |  |  |  |  |

| 0x4004_3000 – 0x4004_3FFF         | EADC0_BA                                          | Enhanced Analog-Digital-Converter 0 (EADC0) Control Registers |  |  |  |  |  |

| 0x4004_5000 – 0x4004_5FFF         | ACMP01_BA                                         | Analog Comparator 0/ 1 Control Registers                      |  |  |  |  |  |

| 0x4004_6000 – 0x4004_6FFF         | OPA_BA                                            | OP Amplifier Control Registers                                |  |  |  |  |  |

| 0x4004_7000 - 0x4004_7FFF         | DAC_BA                                            | DAC Control Registers                                         |  |  |  |  |  |

| 0x4004_B000 – 0x4004_BFFF         | EADC1_BA                                          | Enhanced Analog-Digital-Converter 1 (EADC1) Control Registers |  |  |  |  |  |

| 0x4004_D000 – 0x4004_DFFF         | OTG_BA                                            | OTG Control Registers                                         |  |  |  |  |  |

| 0x4004_F000 - 0x4004_FFFF         | HSOTG_BA                                          | HSOTG Control Registers                                       |  |  |  |  |  |

| 0x4005_0000 – 0x4005_0FFF         | TMR01_BA                                          | Timer0/Timer1 Control Registers                               |  |  |  |  |  |

| 0x4005_1000 - 0x4005_1FFF         | TMR23_BA                                          | Timer2/Timer3 Control Registers                               |  |  |  |  |  |

| 0x4005_8000 - 0x4005_8FFF         | EPWM0_BA                                          | EPWM0 Control Registers                                       |  |  |  |  |  |

| 0x4005_9000 - 0x4005_9FFF         | EPWM1_BA                                          | EPWM1 Control Registers                                       |  |  |  |  |  |

| 0x4005_A000 – 0x4005_AFFF         | BPWM0_BA                                          | BPWM0 Control Registers                                       |  |  |  |  |  |

| 0x4005_B000 – 0x4005_BFFF         | BPWM1_BA                                          | BPWM1 Control Registers                                       |  |  |  |  |  |

| 0x4006_0000 - 0x4006_0FFF         | QSPI0_BA                                          | QSPI0 Control Registers                                       |  |  |  |  |  |

| 0x4006_1000 – 0x4006_1FFF         | SPI0_BA                                           | SPI0 Control Registers                                        |  |  |  |  |  |

| 0x4006_2000 – 0x4006_2FFF         | SPI1_BA                                           | SPI1 Control Registers                                        |  |  |  |  |  |

| 0x4006_3000 - 0x4006_3FFF         | SPI2_BA                                           | SPI2 Control Registers                                        |  |  |  |  |  |

| 0x4006_4000 – 0x4006_4FFF         | SPI3_BA                                           | SPI3 Control Registers                                        |  |  |  |  |  |

| 0x4006_9000 – 0x4006_9FFF         | QSPI1_BA                                          | QSPI1 Control Registers                                       |  |  |  |  |  |

| 0x4007_0000 – 0x4007_0FFF         | UART0_BA                                          | UART0 Control Registers                                       |  |  |  |  |  |

| 0x4007_1000 – 0x4007_1FFF         | UART1_BA                                          | UART1 Control Registers                                       |  |  |  |  |  |

| 0x4007_2000 – 0x4007_2FFF         | UART2_BA                                          | UART2 Control Registers                                       |  |  |  |  |  |

| 0x4007_3000 – 0x4007_3FFF         | UART3_BA                                          | UART3 Control Registers                                       |  |  |  |  |  |

| 0x4007_4000 – 0x4007_4FFF         | UART4_BA                                          | UART4 Control Registers                                       |  |  |  |  |  |

| 0x4007_5000 – 0x4007_5FFF         | UART5_BA                                          | UART5 Control Registers                                       |  |  |  |  |  |

| 0x4007_6000 – 0x4007_6FFF         | UART6_BA                                          | UART6 Control Registers                                       |  |  |  |  |  |

| 0x4007_7000 – 0x4007_7FFF         | UART7_BA                                          | UART7 Control Registers                                       |  |  |  |  |  |

| 0x4008_0000 – 0x4008_0FFF         | I <sup>2</sup> C0_BA                              | I <sup>2</sup> C0 Control Registers                           |  |  |  |  |  |

| 0x4008_1000 – 0x4008_1FFF         | I <sup>2</sup> C1_BA                              | I <sup>2</sup> C1 Control Registers                           |  |  |  |  |  |

| 0x4008_2000 – 0x4008_2FFF         | l <sup>2</sup> C2_BA                              | I <sup>2</sup> C2 Control Registers                           |  |  |  |  |  |

| 0x4009_0000 – 0x4009_0FFF         | SC0_BA                                            | Smartcard Host 0 Control Registers                            |  |  |  |  |  |

| 0x4009_1000 – 0x4009_1FFF                            | SC1_BA   | Smartcard Host 1 Control Registers              |  |  |

|------------------------------------------------------|----------|-------------------------------------------------|--|--|

| 0x4009_2000 – 0x4009_2FFF                            | SC2_BA   | Smartcard Host 2 Control Registers              |  |  |

| 0x4009_3000 – 0x4009_3FFF                            | SC3_BA   | Smartcard Host 3 Control Registers              |  |  |

| 0x400B_0000 – 0x400B_0FFF                            | QEI0_BA  | QEI0 Control Registers                          |  |  |

| 0x400B_1000 – 0x400B_1FFF                            | QEI1_BA  | QEI1 Control Registers                          |  |  |

| 0x400B_4000 - 0x400B_4FFF                            | ECAP0_BA | ECAP0 Control Registers                         |  |  |

| 0x400B_5000 – 0x400B_5FFF                            | ECAP1_BA | ECAP1 Control Registers                         |  |  |

| 0x400B_9000 - 0x400B_9FFF                            | TRNG_BA  | TRNG Control Registers                          |  |  |

| 0x400C_0000 - 0x400C_0FFF                            | USBD_BA  | USB Device Control Register                     |  |  |

| 0x400D_0000 – 0x400D_0FFF                            | USCI0_BA | USCI0 Control Registers                         |  |  |

| 0x400D_1000 – 0x400D_1FFF                            | USCI1_BA | USCI1 Control Registers                         |  |  |

| System Controllers Space (0xE000_E000 ~ 0xE000_EFFF) |          |                                                 |  |  |

| 0xE000_E010 – 0xE000_E0FF                            | SCS_BA   | System Timer Control Registers                  |  |  |

| 0xE000_E100 - 0xE000_ECFF                            | SCS_BA   | External Interrupt Controller Control Registers |  |  |

| 0xE000_ED00 - 0xE000_ED8F                            | SCS_BA   | System Control Registers                        |  |  |

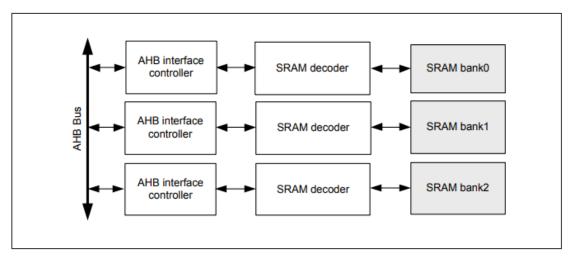

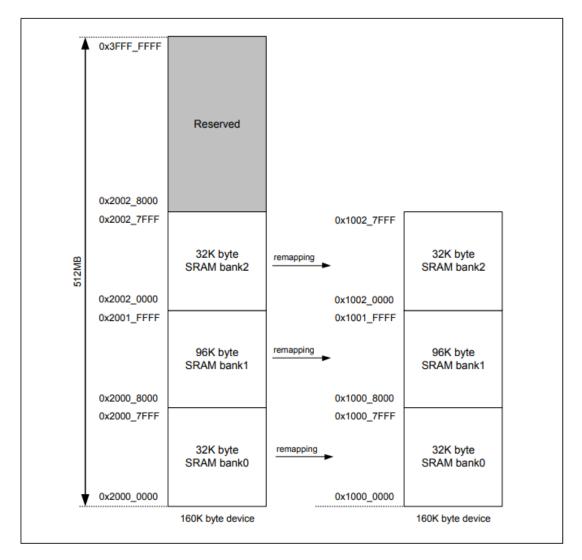

### 4.2.7 SRAM Memory Organization

The ITM-MV8 series supports embedded SRAM with total 160 Kbytes size and the SRAM organization is separated to three banks: SRAM bank0 and SRAM bank1 and SRAM bank2. The first bank has 32 Kbytes address space, the second bank has 96 Kbyte address space and the third bank has 32Kbyte. These three banks address space can be accessed simultaneously. The SRAM bank0 supports parity error check to make sure chip operating more stable. The SRAM bank2 is shared with SPIM cache, it can switch to external SPI Flash cache memory. Note that SRAM bank2 has additional two wait cycles when reading data.

- Supports total 160 Kbytes SRAM

- Supports byte / half word / word write

- Supports fixed 32 Kbytes SRAM bank0 for independent access

- Supports parity error check function for SRAM bank0

- Supports oversize response error

- Supports remap address to 0x1000\_0000

Figure 4.2-9 SRAM Block Diagram

|            | 160 Kbytes Device |    | 128 Kbytes Device |    | 64KB Device |    | Read Access     |       |     |

|------------|-------------------|----|-------------------|----|-------------|----|-----------------|-------|-----|

| SRAM bank0 | 0x2000_0000       | ~  | 0x2000_0000       | ~  | 0x2000_0000 | ~  | Zero wait       | cycle | for |

|            | 0x2000_7FFF       | or | 0x2000_7FFF       | or | 0x2000_7FFF | or | continuous acc  | ess   |     |

|            | 0x1000_0000       | ~  | 0x1000_0000       | ~  | 0x1000_0000 | ~  |                 |       |     |

|            | 0x1000_7FFF       |    | 0x1000_7FFF       |    | 0x1000_7FFF |    |                 |       |     |

| SRAM bank1 | 0x2000_8000       | ~  | 0x2000_8000       | ~  | 0x2000_8000 | ~  | Zero wait       | cycle | for |

|            | 0x2001_FFFF       | or | 0x2001_FFFF       | or | 0x2000_FFFF | or | continuous acc  | ess   |     |

|            | 0x1000_8000       | ~  | 0x1000_8000       | ~  | 0x1000_8000 | ~  |                 |       |     |

|            | 0x1001_FFFF       |    | 0x1001_FFFF       |    | 0x1000_FFFF |    |                 |       |     |

| SRAM bank2 | 0x2002_0000       | ~  |                   |    |             |    | Two wait cycles | 3     |     |

|            | 0x2002_7FFF       | or |                   |    |             |    |                 |       |     |

|            | 0x1002_0000       | ~  |                   |    |             |    |                 |       |     |

|            | 0x1002_7FFF       |    |                   |    |             |    |                 |       |     |

Table 4.2-8 SRAM Organization

The address of each bank is remapping from 0x2000\_0000 to 0x1000\_0000. CPU can access SRAM bank0 through 0x2000\_0000 to 0x2000\_7FFF or 0x1000\_0000 to

0x1000\_7FFF, and access SRAM bank1 through 0x2000\_8000 to 0x2001\_FFFF or 0x1000\_8000 to 0x1001\_FFFF, and access SRAM bank2 through 0x2002\_0000 to 0x2002\_7FFF or 0x1002\_0000 to 0x1002\_7FFF.

When setting the control register CCMEN(SPIM\_CTL1[2]) to 0, SRAM bank2 is switched to external SPI Flash cache memory. In this case, the SRAM bank2 can't be accessed as general SRAM. If user access SRAM bank2 by AHB bus master, the SPI Flash controller will send error response via HRESP AHB bus signal to bus master.

Figure 4.2-10 SRAM Memory Organization

SRAM bank0 has byte parity error check function. When CPU is accessing SRAM bank0, the parity error checking mechanism is dynamic operating. As parity error occurred, the PERRIF (SYS\_SRAM\_STATUS[0]) will be asserted to 1 and the SYS\_SRAM\_ERRADDR register will recode the address with parity error. Chip will enter interrupt when SRAM parity error occurred if PERRIEN (SYS\_SRAM\_INTCTL[0]) is set to 1. When SRAM parity error occurred, chip will stop detecting SRAM parity

error until user writes 1 to clear the PERRIF(SYS\_SRAM\_STATUS[0]) bit.

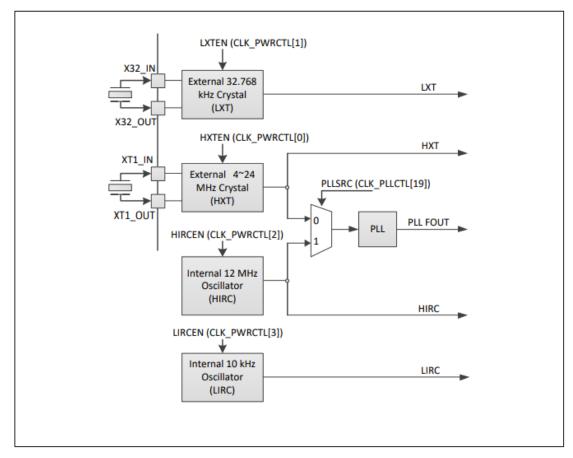

#### 4.2.8 HIRC Auto Trim

This chip supports auto-trim function: the HIRC trim (12 MHz RC oscillator) and HIRC trim (48 MHz RC oscillator,), according to the accurate LXT (32.768 kHz crystal oscillator) or internal USB synchronous mode, automatically gets accurate HIRC output frequency, 0.25 % deviation within all temperature ranges. For instance, the system needs an accurate 12 MHz clock. In such case, if neither using use PLL as the system clock source nor soldering 32.768 kHz crystal in system, user has to set REFCKSEL (SYS\_IRCTCTL[10] reference clock selection) to "1", set FREQSEL (SYS\_IRCTCTL[1:0] trim frequency selection) to "01", and the auto-trim function will be enabled. Interrupt status bit FREQLOCK (SYS\_IRCTISTS[8] HIRC frequency lock status) "1" indicates the HIRC output frequency is accurate within

0.25% deviation.